![]() UVOD U SERIJSKI PORT

UVOD U SERIJSKI PORT

Serijski port PC računara koristi se za serijski prenos podataka (bit po bit)

i samim tim je sporiji od paralelnog porta. Uređaji koji koriste serijsku

komunikaciju koriste dve vrste kablova i to: DCE(Data Communications Equipment)

i DTE(Data Terminal Equipment). DCE koriste modemi, ploteri i sl. dok se DTE

koristi za vezu između PC računara. Električne osobine serijskog porta su

sadržane u EIA(Electronics Industry Association) RS232C standardu čiji su

parametri sledeći:

1. Logička nula

"SPACE" nalazi se u opsegu napona +3 do +25 Volti

2. Logička jedinica "MARK" je u opsegu

-3 do - 25 Volti

3. Oblast između -3 do + 3 Volta nije definisana

4. Napon na kolu ne sme da pređe 25 Volti u odnosu

na masu(GND)

5. Struja kola ne sme preći 500 mA

Pored RS232C standarda postoje i novije verzije EIA-232D

i EIA-232E koje su objavljene 1987 i 1991

godine. Serijski port koristi dve vrste konektora i to D-SUB 25 pinski i D-SUB

9 pinski konektor. Oblik konektora i raspored pinova na njima kao i glavni

signali na pojedinim pinovima dati su na donjoj slici i tabeli.

|

DSUB-25 |

DSUB-9 |

|

DSUB-25 |

DSUB-9 |

Signal |

Opis signala |

|

pin 2 |

pin 3 |

TD |

Transmit Data |

|

pin 3 |

pin 2 |

RD |

Receive Data |

|

pin 4 |

pin 7 |

RTS |

Request ToSend |

|

pin 5 |

pin 8 |

CTS |

Clear To Send |

|

pin 6 |

pin 6 |

DSR |

Data Set Ready |

|

pin 7 |

pin 5 |

SG |

Signal Ground |

|

pin 8 |

pin 1 |

CD |

Carrier Detect |

|

pin 20 |

pin 4 |

DTR |

Data Terminal Ready |

|

pin 22 |

pin 9 |

RI |

Ring Indikator |

Značenje pojedinih signala je sledeće:

|

Signal |

Opis signala |

Značenje signala |

|

TD |

Transmit Data |

Serijski izlaz podataka(TXD) |

|

RD |

Receive Data |

Serijski ulaz podataka(RXD) |

|

RTS |

Request ToSend |

Indicira da je modem spreman za razmenu podataka |

|

CTS |

Clear To Send |

Kada modem detektuje signal "Carrier" od modema sa druge strane

linije, onda ona postaje aktivna |

|

DSR |

Data Set Ready |

DCE signalizira da je spreman za rad |

|

SG |

Signal Ground |

Masa |

|

CD |

Carrier Detect |

DCE javlja da je veza uspostavljena |

|

DTR |

Data Terminal Ready |

Indicira DCE uređaju da je DTE spreman |

|

RI |

Ring Indikator |

Signalizira da je detektovan signal "zvona" na telefonskoj

liniji |

Oblik signala RS232 standarda dat je na donjoj slici:

Kada nema slanja podatka tj. linija je slobodna označeno je MARK naponom.

Prenos počinje kada linija pređe u SPACE stanje što predstavlja START bit. Iza

start bita dolaze bitovi podataka i to tako da je jedinica predstavljena

negativnim naponom a nula pozitivnim. Ovo je najčešće u suprotnosti sa

ustaljenom logikom da je +5 V logička jedinica, a 0 V logička nula. Problem

rešava prijemno kolo konvertujući napone tako da su prilagođeni naponima

interfejsa koji se koristi. Posle bita podatka dolazi bit pariteta koji se

koristi za detekciju greške u prenosu. Iza bita pariteta signal se postavlja u

MARK stanje što označava početak STOP bita. Prema RS232 standardu broj stop

bitova može biti: 1, 1.5 ili 2. Nakon završetka STOP bitova linija je spremna

za slanje novog karaktera. PC računari koriste kao DATA bite najčešće 7 ili 8

bita. Između slanja dva karaktera linija se nalazi u MARK stanju, a u toku

prenosa više puta prelazi iz MARK u SPACE stanje u zavisnosti od broja jedinica

i nula. To znači da se linija može nalaziti

u SPACE stanju najviše u slučaju kada karakter sadrži sve nule. Ova osobina

prenosa upotrebljena je za uvođenje specijalnog znaka nazvanog BREAK(prekid).

Ovaj se signal koristi kako bi prijemniku data signalizacija da je došlo do

problema u slanju podataka.

Serijski prenos počinje tako da predajna strana šalje

prijemnoj strani signal RTS - zahtev za slanjem, dok prijemnik ako je spreman

za prijem odgovara signalom CTS - spreman za prijem. Predajnik zatim šalje

podatke prijemniku. Nakon prijema podataka prijemnik proverava da li su podaci

primljeni bez greške i za to vreme javlja predajniku da je zauzet. Ako su

podaci primljeni bez greške, prijemnik šalje predajniku signal potvrde

ACK(Acknowledgment - ASCII 6), a u slučaju ako se pojavila neka greška, šalje

signal negativne potvrde NAK(ASCII 21). Zavisno od upotrebljenog protokola,

odgovor predajnika na dobijeni NAK signal može biti ponovno slanje podataka.

Protokol za prenos može se izvesti na dva načina i to:

hardverski i softverski. Za realizaciju hardverskog protokola neophodno je da

postoje linije: RTS, CTS i linija za prenos bitova poruke. Softverska

realizacija koristi umesto linija RTS i CTS, ASCII znakove XON i XOFF (nazivaju

su i DC1 i DC3), zbog čega je umesto tri dovoljna samo jedna linija. Kada se

primenjuje ovaj protokol prijemnici i na predaji i prijemu proveravaju svaki

prispeli znak radi utvrđivanja da li je to XON, XOFF ili podatak. Strana koja

ne može da primi karakter kao indikator tog stanja drugoj strani šalje XOFF

znak.

Prilikom serijskog prenosa podataka moguća je pojava sledećih vrsta

grešaka:

·

Greška

uokvirenja(framing error). Do ove greške dolazi u slučaju kada prijemnik

očekuje STOP bit ali se on ne pojavljuje.

·

Greška

prekoračenja(overrun error). Nastaje kada se pojavljuje novi znak u prijemniku

a prethodni nije upotpunosti primljen.

·

Greška

pariteta(parity error). Nastaje kada bit pariteta ne odogovara stanju bitova u

bitovima podatka.

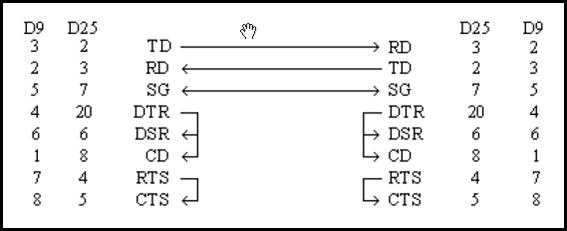

Standardno za vezu dva PC računara koristi se takozvani Null Modem kabal čiji je raspored pinova

dat na donjoj slici:

Iz slike se vidi da su i na prijemnoj

i predajnoj strani spojeni signali DTR, DSR i CD kao i RTS i CTS, dok su

signali TD i RD ukršteni.

Za testiranje serijskog porta i izradu

programa koristi se kabal sa zatvoreno

petljom (LoopBack) prikazan na donjoj slici:

Serijska komunikacija se kod PC

računara izvodi upotrebom Intelovog UART kola 8250 kod XT ili 16450 kod AT

računara. Oba su kola slična s tim što kolo 16450 ima neka poboljšanja. Kolo

8250 ima 10 dok kolo 16450 ima 12 programibilnih jednobajtnih registara. Svaki

port (COM1 i COM2) ima po jedno UART kolo koja se vezuju na linije prekida IRQ3

i IRQ4. Standardno se koriste dva porta a moguće je i više sa adresama i IRQ

prem donjoj tabeli:

|

Naziv |

Adresa |

IRQ |

|

COM 1 |

3F8 |

4 |

|

COM 2 |

2F8 |

3 |

|

COM 3 |

3E8 |

4 |

|

COM 4 |

2E8 |

3 |

Bazne adrese COM portova nalaze u BIOS-u na adresama datim u donjoj tabeli:

|

Startna adresa |

Opis |

|

0000:0400 |

Početna adresa COM1 |

|

0000:0402 |

Početna adresa COM2 |

|

0000:0404 |

Početna adresa COM3 |

|

0000:0406 |

Početna adresa COM4 |

Serijski port upotrebljava u svom radu

sledeću grupu registara:

|

Bazna Adresa |

DLAB |

Čitanje/Pisanje |

Skraćeni naziv |

Naziv registra |

|

+ 0 |

=0 |

Pisanje |

THR |

Transmitter Holding Buffer |

|

=0 |

Čitanje |

RDR |

Receiver Buffer |

|

|

=1 |

Čitanje/Pisanje |

DLL |

Divisor Latch Niži Bajt |

|

|

+1 |

=0 |

Čitanje/Pisanje |

IER |

Interrupt Enable Register |

|

=1 |

Čitanje/Pisanje |

DLH |

Divisor Latch Viši Bajt |

|

|

+2 |

- |

Čitanje |

IIR |

Interrupt Identification Register |

|

- |

Pisanje |

FCR |

FIFO Control Register |

|

|

+3 |

- |

Čitanje/Pisanje |

LCR |

Line Control Register |

|

+4 |

- |

Čitanje/Pisanje |

MCR |

Modem Control Register |

|

+5 |

- |

Čitanje |

LSR |

Line Status Register |

|

+6 |

- |

Čitanje |

MSR |

Modem Status Register |

|

+7 |

- |

Čitanje/Pisanje |

- |

Scratch Register |

Transmitter

Holding(THR) i Receiver Buffer(RDR) registar su registri podatka. Prvom

se pristupa prilikom slanja karaktera na port, a drugom u trenutku čitanja

karaktera sa porta. Kako se ove dve operacije međusobno isključuju to je

nemoguće da dođe do kolizije. Registar THR

sadrži bajt koji treba poslati na liniju. Podatak se može upisati kada peti bit

Line Status Registra naznači da je on prazan. RDR registar sadrži poslednji primljeni bajt sa linije. Sadržaj

ovog registra se može pročitati kada je

nulti bit Line Status Registra označen da je primljen. Na offsetu 0 nalazi se i registar Divisor

Latch Niži Bajt u slučaju kada je DLAB=1.

Ovaj se registar kao i sledeći Divisor Latch Viši Bajt koriste se samo u

procesu inicijalizacije UART-a. Proces inicijalizacije se označava

setovanjem sedmog bita u Line Control

Registru(DLAB), tako da ni u ovom

slučaju nemože doći do dvostrukog tumačenja. Za različite brzine prenosa

izražene brojem bita u sekudni(bps) moramo znati trajanje signala koji

reprezentuje jedan bit. Ta se konstanta ne definiše direktno već preko pomoćne

vrednosti koja se dobije iz formula:

Divisor Latch=(clock)/(16 x bps) ili

Divisor Latch=(1843200/(16 x bps) ili

Divisor Latch=(115200)/(bps)

gde clock

predstavlja frekvenciju internog takta UARTa koja je 1.8432 Mhz, a bps je

željena brzina prenosa. Divisor Latch je broj kojim se deli takt UART kola da

se dobije dužina trajanja jednog bita pri željenoj brzini prenosa. Taj se broj

raspoređuje na niži(DLL) i viši(DLH) bajt što je dato u donjoj tabeli.

|

Brzina (bps) |

Delilac |

DLH |

DLL |

|

50 |

2304 |

09h |

00h |

|

300 |

384 |

01h |

80h |

|

600 |

192 |

00h |

C0h |

|

2400 |

48 |

00h |

30h |

|

4800 |

24 |

00h |

18h |

|

9600 |

12 |

00h |

0Ch |

|

19200 |

6 |

00h |

06h |

|

38400 |

3 |

00h |

03h |

|

57600 |

2 |

00h |

02h |

|

115200 |

1 |

00h |

01h |

Struktura Interrupt Enable Registra(IER) data je u donjoj tabeli:

|

Bit |

Opis |

|

Bit 7 |

Ne koristi se |

|

Bit 6 |

Ne koristi se |

|

Bit 5 |

Omogućava Low Power Mod(16750) |

|

Bit 4 |

Omogućava Sleep Mod(16750) |

|

Bit 3 |

Omogućava Modem Status Interapt |

|

Bit 2 |

Omogućava Receiver Line Status Interapt |

|

Bit 1 |

Omogućava Transmitter Holding Registar

Interapt kada je prazan |

|

Bit 0 |

Omogućava Received Data Interapt |

Ovim registrom se određuje na koji će

tip prekida UART kolo reagovati. Može se dozvoliti pojava i više tipova

prekida. Prekid se generiše kada se ispuni neki od uslova iz date tabele. Tada

se postavalja odgovarajući bit iz prve kolone kao indikator pojave prekida.

Nakon obrade prekida postavljeni bit se resetuje i UART je spreman da prihvati

sledeći prekid.

Interrupt Identification Register(IIR) ima strukturu kao u donjoj tabeli:

|

Bit |

Opis |

||

|

Bitovi 6 i 7 |

Bit 6 |

Bit 7 |

|

|

0 |

0 |

Ne koristi

se FIFO |

|

|

0 |

1 |

FIFO je

omogućen ali se ne može koristiti |

|

|

1 |

1 |

FIFO je

omogućen |

|

|

Bit 5 |

64 Bajtni

FIFO je omogućen(samo za 16750) |

||

|

Bit 4 |

Rezervisan |

||

|

Bit 3 |

0 |

Rezervisan

za 8250 i 16450 |

|

|

1 |

16550

Time-out Interapt je u toku |

||

|

Bitovi 1 i 2 |

Bit 2 |

Bit 1 |

|

|

0 |

0 |

Modem

Status Interapt |

|

|

0 |

1 |

THR

interapt registar kada je prazan |

|

|

1 |

0 |

Podatak je

primljen |

|

|

1 |

1 |

Primljeni

Line Status Interapt |

|

|

Bit 0 |

0 |

Prekid je u

toku |

|

|

|

1 |

Ne postoje

prekidi |

|

Na osnovu ovog registra komunikacioni

programi određuju tip prekida koji se pojavio.

FIFO Control Registar(FCR) ima strukturu kao u donjoj tabeli:

|

Bit |

Opis |

||

|

Bitovi 6 i 7 |

Bit 6 |

Bit 7 |

Nivo

Interapta |

|

0 |

0 |

1 Bajt |

|

|

0 |

1 |

2 Bajta |

|

|

1 |

0 |

8 Bajta |

|

|

1 |

1 |

16 Bajta |

|

|

Bit 5 |

64 Bajtni

FIFO je omogućen(samo za 16750) |

||

|

Bit 4 |

Rezervisan |

||

|

Bit 3 |

Izbor DMA

moda |

||

|

Bit 2 |

Briše FIFO

slanja |

||

|

Bit 1 |

Briše FIFO

prijema |

||

|

Bit 0 |

Omogućav

FIFO metod |

||

FIFO je registar u koji se može samo

upisivati. Koristi se za kontrolu FIFO bafera koji postoji na UART-ima 16550 i

više. Postavljanjem bita 0 omogućuje predajni i prijemni FIFO a njegovim

resetovanjem se zabranjuje. Bitovi 1 i 2 kontrolišu brisanje prijemnog i

predajnog FIFO bafera. Setovanjem ovih bitova na 1 će samo obrisati sadržaj

FIFO bafera i neće uticati na šift registar. Ova dva bita se sami resetuju i

zato nemoramo bitove setovati na nulu po

završetku. Bit 3 omogućava DMA selektovanje DMA moda koji se može naći na

UART-ima 16550 i više. Bitovi 6 i 7 se koriste da se postavi nivo okidanja na

primajući FIFO. Naprimer ako je bit 7 postavljen na 1 i bit 6 na 0 onda je nivo

okidanja setovan na osam bajtova. Kada je primljeno 8 bajtova podataka u

primajućem FIFO onda je Received Data Interapt postavljen u IIR registru.

Line

Control Registar(LCR) ima strukturu

kao u donoj tabeli:

|

Bit |

Opis |

|||

|

Bit 7 |

1 |

DLAB bit |

||

|

0 |

Omogućen

pristup THR, RDR i IER registru |

|||

|

Bit 6 |

0 -

Zabranjen Break signal, 1 - Omogućen |

|||

|

Bitovi 3 : 5 |

Bit 5 |

Bit 4 |

Bit 3 |

Izbor

pariteta |

|

X |

X |

0 |

Bez

pariteta |

|

|

0 |

0 |

1 |

Neparan(Odd)

paritet |

|

|

0 |

1 |

1 |

Paran(Even)

paritet |

|

|

1 |

0 |

1 |

MARK |

|

|

1 |

1 |

1 |

SPACE |

|

|

Bit 2 |

Dužina stop

bita |

|||

|

0 |

Jedan stop

bit |

|||

|

1 |

2 stop bita

ako je dužina podatka 6, 7 ili 8 bita, odnosno 1.5 stop bit za podatak dužine

5 bita |

|||

|

Bitovi 0:1 |

Bit 1 |

Bit 0 |

Dužina

podatka u bitima |

|

|

0 |

0 |

5 bita |

||

|

0 |

1 |

6 bita |

||

|

1 |

0 |

7 bita |

||

|

1 |

1 |

8 bita |

||

Ovaj registar omogućava postavljanje

nekih od parametara veze kao i režim rada registara THR, RDR, DLL i DLH. Režim rada navedenih registara određuje njegov sedmi bit DLAB(Divisor Latch Access Byte).

Modem Control Registar(MCR) koristi sledeću strukturu:

|

Bit |

Opis |

|

Bit 7 |

Ne koristi se |

|

Bit 6 |

Ne koristi se |

|

Bit 5 |

Autoflow kontrola omogućena(samo za 16750) |

|

Bit 4 |

Bit povratne sprege |

|

Bit 3 |

Korisnički izlaz #1 |

|

Bit 2 |

Korisnički izlaz #2 |

|

Bit 1 |

RTS linija aktivna |

|

Bit 0 |

DTR linija aktivna |

DTR linija signalizira modemu da je

računar spreman da od njega primi karakter, dok linija RTS signalizira modemu

da je računar spreman da mu pošalje podatak. Korisnički izlaz#1 normalno nije

spojen ali se na nekim karticama koristi za prebacivanje između 1.8432 Mhz

kristala i 4 Mhz kristala koje se koristi za MIDI. Korisnički izlaz#2 se

koristi za spajanje vanjskih kola koja kontrolišu UART-CPU interept procese.

Line Status Regitar(LSR) koristi sledeću strukturu:

|

Bit |

Opis |

|

Bit 7 |

Greška u prijemnom FIFO |

|

Bit 6 |

Prazan Data Holding Registar |

|

Bit 5 |

Prazan THR registar i može se slati sledeći znak |

|

Bit 4 |

Detektovan signal prekida (Break) |

|

Bit 3 |

Greška uokvirenja(Framing error) |

|

Bit 2 |

Greška pariteta(Parity error) |

|

Bit 1 |

Greška prekoračenja(Overrun error) |

|

Bit 0 |

Podatak je primljen i bajt se nalazi u RDR |

Ovaj registar ima prevashodno

namenu da daje izveštaj o stanju na komunikacionoj liniji.

Modem Status Registar(MSR) ima sledeću strukturu:

|

Bit |

Opis |

|

Bit 7 |

Aktivira "Data Carrie Detect" (DCD) |

|

Bit 6 |

Aktivira "Ring Indicator"(RI) |

|

Bit 5 |

Aktivira"Data Set Ready"(DSR) |

|

Bit 4 |

Aktivira"Clear To Send"(CTS) |

|

Bit 3 |

Promena u "Data Carrier Detect"(DCD) |

|

Bit 2 |

Promena u "Ring Indicator"(RI) |

|

Bit 1 |

Promena u "Data Set Ready"(DSR) |

|

Bit 0 |

Promena u "Clear To Send"(CTS) |

Status modema zavisi pre svega

od toga da li je neka linija aktivna ili nije

i da li se status pojedine linije promenio od poslednjeg čitanja ovog

registra.

http://vojo.milanovic.org

© Copyright, 2003 Milanović Vojo

All Rights Reserved.